PDF) A super-dynamic flip-flop circuit for broadband applications up to 24 Gbit/s utilizing production-level 0.2-μm GaAs MESFETs | Taiichi Otsuji - Academia.edu

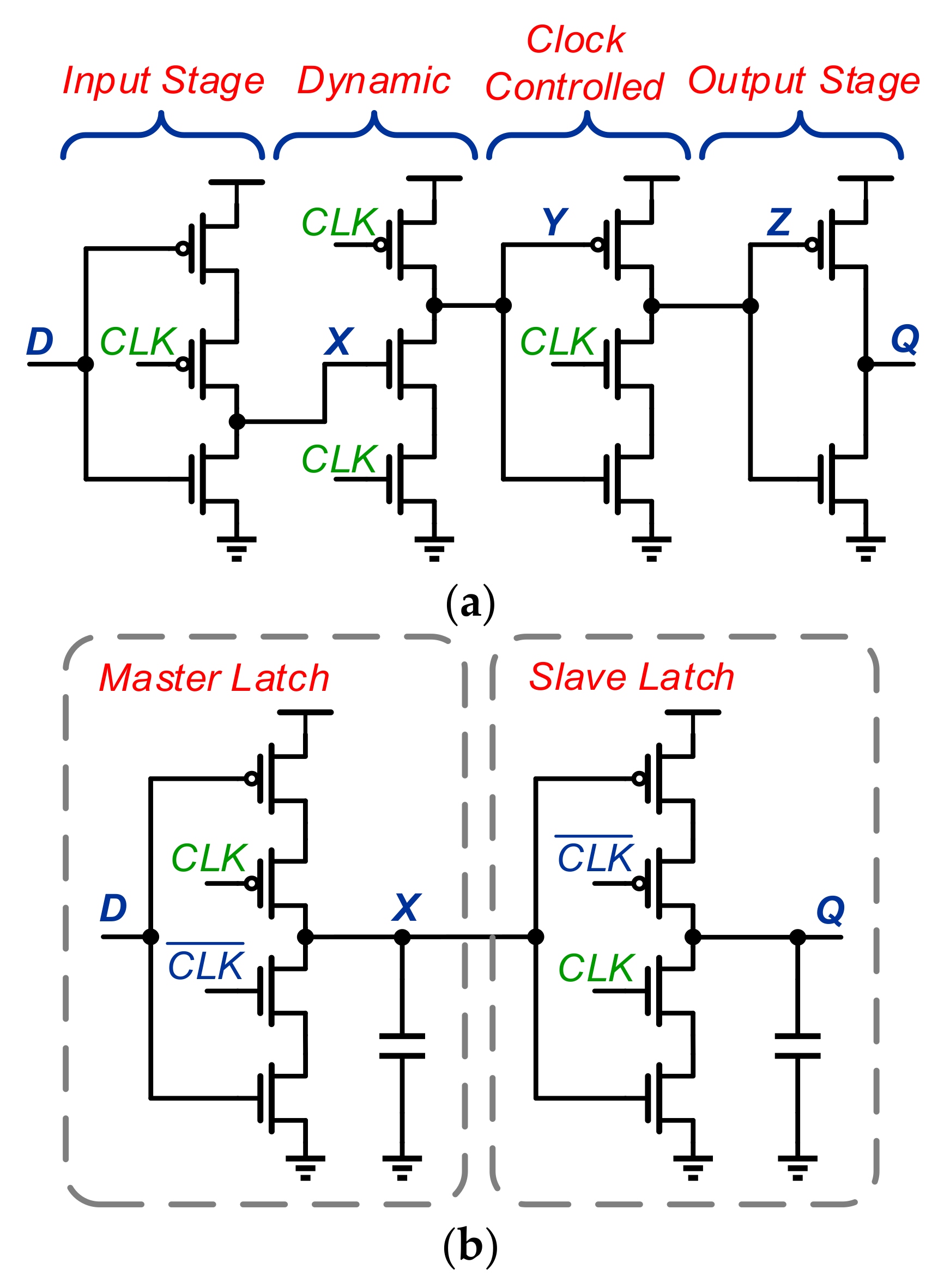

![PDF] A new family of semidynamic and dynamic flip-flops with embedded logic for high-performance processors | Semantic Scholar PDF] A new family of semidynamic and dynamic flip-flops with embedded logic for high-performance processors | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/12d140770677c29db0db7035ac022baf127a1f77/1-Figure1-1.png)

PDF] A new family of semidynamic and dynamic flip-flops with embedded logic for high-performance processors | Semantic Scholar

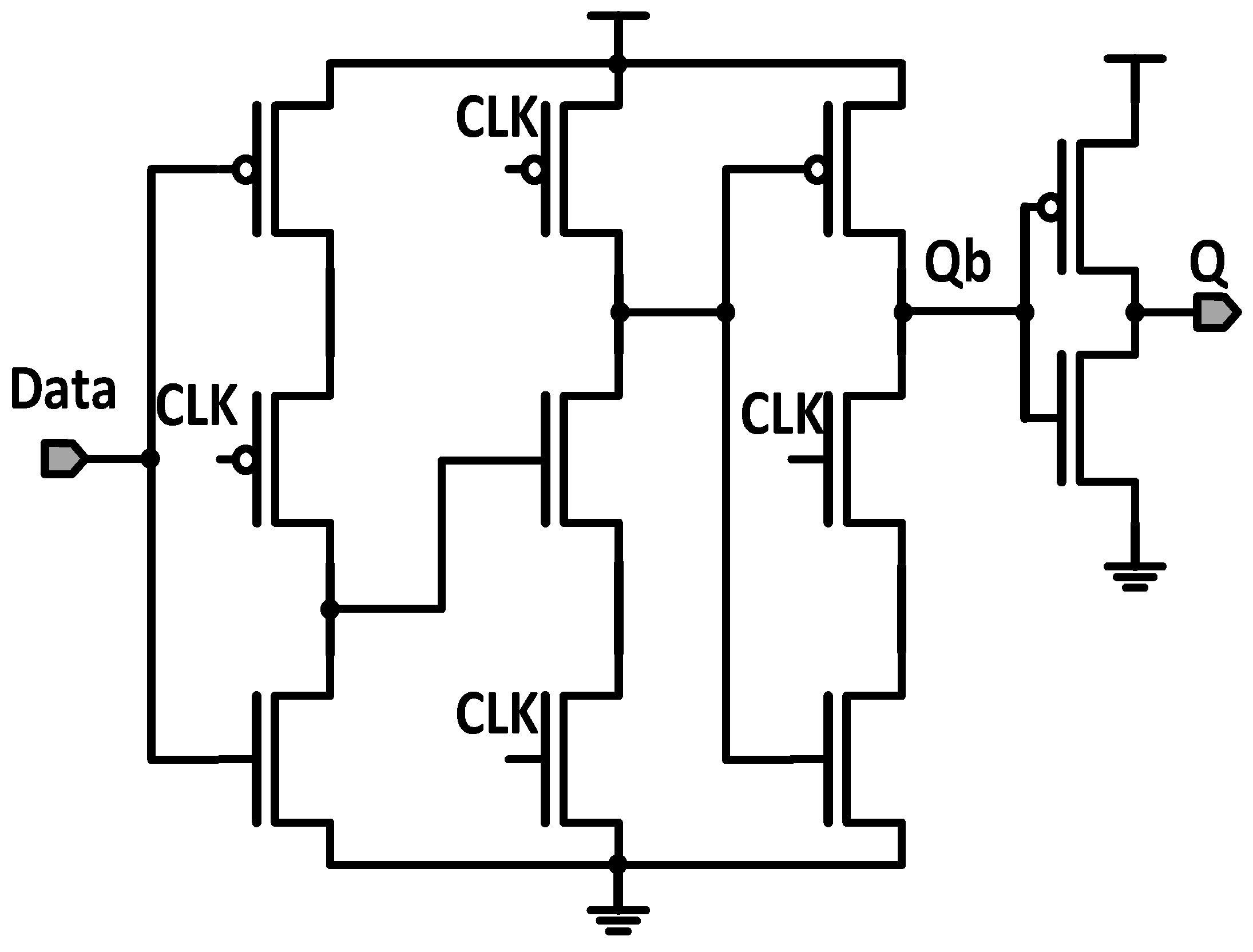

Figure 3 from A New Dynamic Floating Input D Flip-Flop (DFIDFF) for High Speed and Ultra Low Voltage Divided-by 4/5 Prescaler | Semantic Scholar

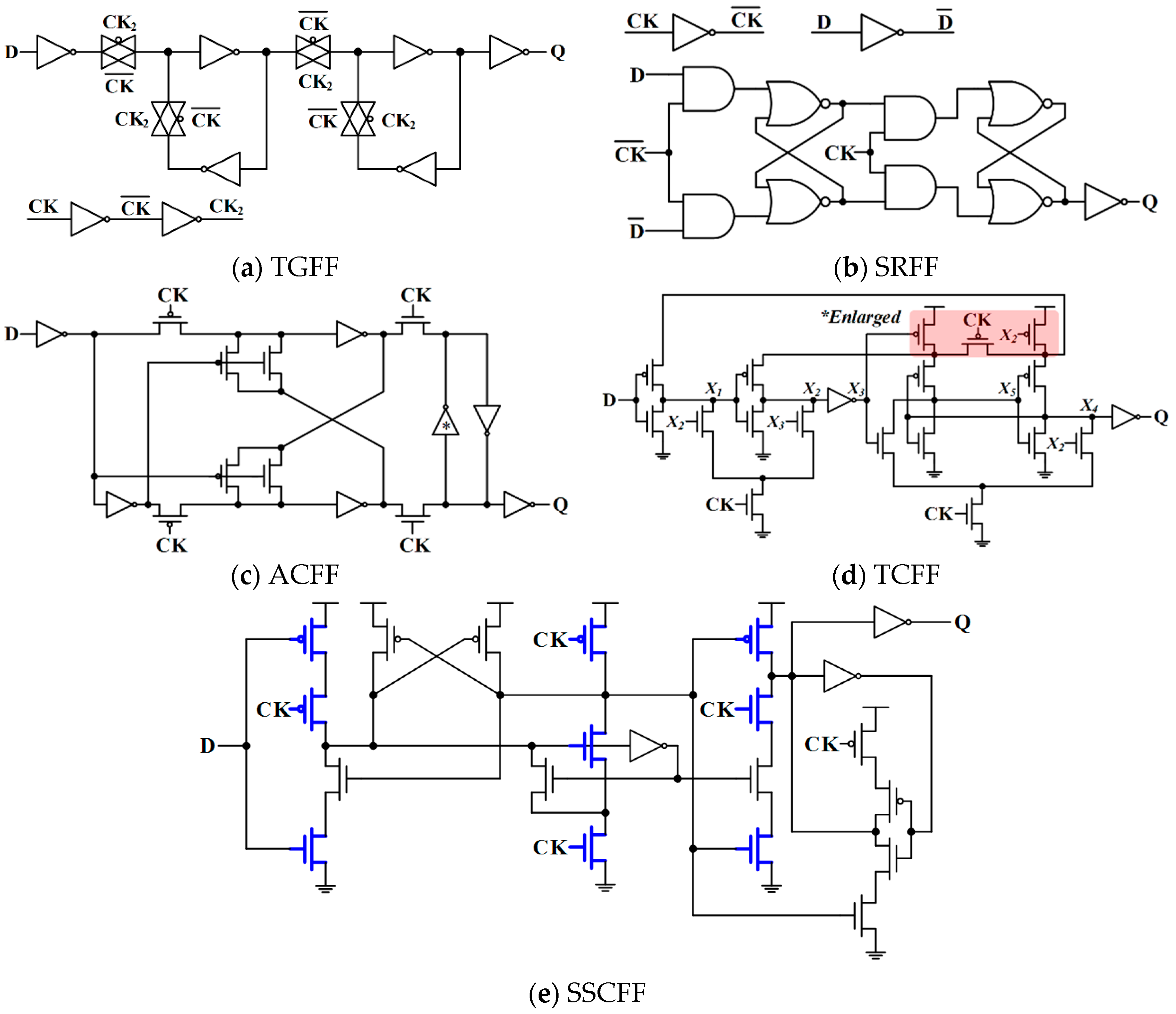

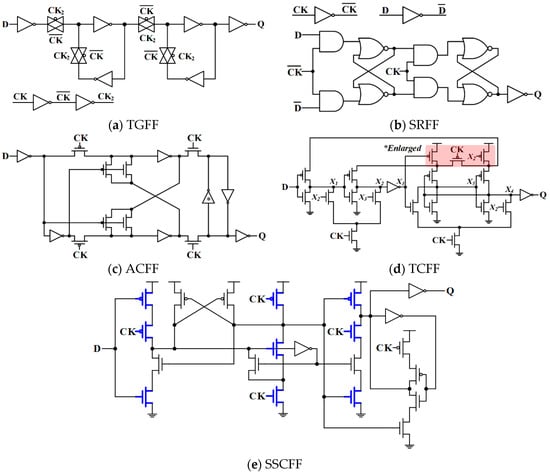

Three different flip-flop architectures. Dynamic MSFFs: (a)TG-MSFF and... | Download Scientific Diagram

Electronics | Free Full-Text | A Novel Radiation-Hardened CCDM-TSPC Compared with Seven Well-Known RHBD Flip-Flops in 180 nm CMOS Process

Electronics | Free Full-Text | Design of a Dual Change-Sensing 24T Flip-Flop in 65 nm CMOS Technology for Ultra Low-Power System Chips

Low Power Paradigm Featuring Dual Dynamic Node Pulsed Hybrid Flip-Flop With Dual Mode Logic and Clock Gating | Semantic Scholar

![PDF] Semi-dynamic and dynamic flip-flops with embedded logic | Semantic Scholar PDF] Semi-dynamic and dynamic flip-flops with embedded logic | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/710f2dc70f27c6aebe01f28fdca059a92698872f/2-Figure2-1.png)